# German Jordanian University Department of Communication Engineering Digital Communication Systems Lab CME 313-Lab

Experiment 3

Pulse Code Modulation

Eng. Anas Alashqar Dr. Ala' Khalifeh **Pulse Code Modulation**

# **Objectives:**

After this experiment the student should be able to:

- 1. Recognize the various processes of PCM encoding and decoding.

- **2.** Realize the structure of the PCM stream.

- **3.** Appreciate the importance of data structure and synchronization.

# **Introduction:**

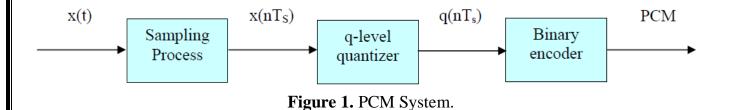

Pulse Code Modulation (PCM) is a method of converting an analog signal into a digital signal (A/D conversion). This is achieved by a PCM encoder via three operations in sequence: sampling, quantization and coding as shown in the Figure 1.

A step-by-step description of the operations of a standard PCM encoder is as follows:

- 1. The encoder is driven by a TTL clock.

- 2. The input analog message is sampled periodically. The sample rate is determined by the external clock and the number of bits per PCM frame.

- 3. Each sample amplitude is compared with a finite set of amplitude levels, called quantization levels. These are distributed within the range  $\pm$  V volts.

- 4. Each sample is assigned a digital (binary) codeword representing the number associated with the quantizing level which is closest to the sample amplitude. The number of bits 'n' in the digital codeword and the number of quantizing levels L are related by the equation  $L=2^n$ .

- 5. The codeword is assembled into a time frame, together with other bits as may be required. In many commercial systems, a single extra bit is added in the least significant bit position. This is alternately a "0" or a "1". These bits are used by subsequent decoders for frame synchronization. The frame is transmitted serially.

Upon reception of a PCM sequence, the PCM decoder:

- 1. extracts a frame synchronization signal FS from the data itself (from the embedded alternate ones and zeros in the LSB position), or uses an FS signal borrowed from the transmitter.

- 2. extracts the binary number, which is the coded (and quantized) amplitude of the sample.

- 3. identifies the quantization level which this number represents.

- 4. generates a voltage proportional to this amplitude level.

- 5. presents this voltage to the output Vout. The voltage appears at Vout for the duration of the sampling period.

Note that, it is not possible to recover a distortionless message from these samples. They are flat top, rather than natural samples. The decoder itself has introduced no distortion of the received signal, but the signal from the PCM encoder is already an inexact version of the signal at the input of the encoder. Message reconstruction can be improved by low pass filtering.

### **PCM Modules**

The input to the PCM ENCODER is an analog message. The sampling rate of the module is defined by (but not equal to) the CLK input, which sets a limit on the maximum allowable message bandwidth, according to Nyquist Sampling Theorem. The dynamic range of the quantizer is designed for the range  $\pm 2.0$  volts, therefore the input message amplitude must be held within this range. We go briefly over each of the input and output connections which will be used in this experiment.

- Digitizing Scheme Select: a three-position toggle switch which selects the 4-bit or 7-bit linear encoding scheme; or the 4-bit companding scheme.

- FS: frame synchronization, a signal indicating the end of each data frame.

- Vin: the analog signal to be encoded.

- PCM DATA: the output data stream.

- CLK: a TTL input serves as the Master Clock for the module.

Clock rate of this module must be 10 kHz or less (manufacture limitation). For this experiment we will use the 8.333 kHz TTL signal from the Master Clock module.

The decoder is driven by an external clock, borrowed from, and so synchronized to, that of the encoder. Frame synchronization may be achieved either by extracting the FS signal from the embedded information in the received data, or by borrowing it externally from the encoder (connecting direct wire between transmitter and receiver). A toggle switch (FS SELECT) in the PCM DECODER allows switching between the two modes.

Though an external signal can be used for demonstrating the PCM operation, the PCM encoder is equipped with test periodic signals (SYNC MESSAGE) of frequencies which are fraction of the clock rate. These signals are synchronized with the clock and, therefore, provide improved triggering. The frequency of these signals can be set from a dip switch SW2 on the board of the PCM Encoder. Note that these signals are not pure sinusoids.

### PCM StreamStructure

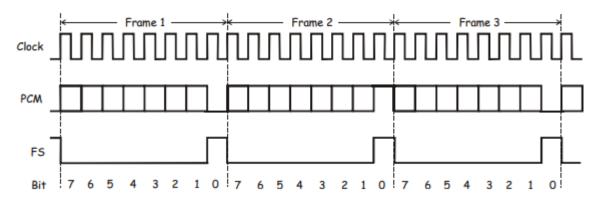

Each binary word is arranged in a time frame. The time frame contains eight slots of equal length, and is eight clock periods long. The slots, from first to last, are numbered 7 through 0. These slots contain the bits of a binary word. The least significant bit (LSB) is contained in slot 0. See Figure 2.

**Figure2.** PCM Encoder Timing Frame.

The LSB consists of alternating ones and zeros. These are placed (embedded) in the frame by the encoder itself, and cannot be modified by the user. They are used by subsequent decoders to determine the location of each frame in the data stream, and its length.

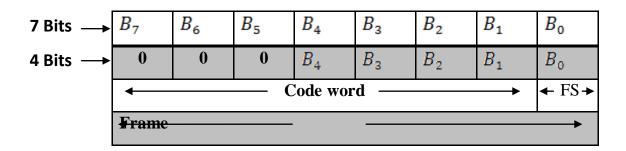

The remaining seven slots are available for the bits of the binary codeword. Thus the system is capable of a resolution of a maximum of seven bits (128 levels). This resolution, for purposes of experiment, can be reduced to four bits (by front panel toggle switch). The 4-bit mode uses only five of the available eight slots - one for the embedded frame synchronization bits, and the remaining four for the binary codeword (in slots 4, 3, 2, and 1). See Figure 3.

**Figure.3** Frame structure for 7-bit and 4-bit words.

# Lab Work

# Modules:

AUDIO OSCILLATOR, PCM ENCODER, PCM DECODER.

### Part I: PCM Frame Structure

- **1.** Patch the 8.333 kHz TTL Clock from the Master Signal module to the CLK input of the PCM Encoder.

- **2.** On one of the oscilloscope channels display the frame synchronization signal FS. Adjust the sweep speed (Time/Division) to show three frame markers.

- **3.** On the second oscilloscope channel display the CLK signal.

- **4.** Place the two waveform on the top of each other so that they can be easily compared,

- Save the obtained signal in step 4 in your lab sheets.

- What is the frame duration? Bit duration? Codeword duration?

- What is the sampling rate of the PCM Encoder? Is it appropriate to sample a speech signal? Why?

### Part II: Quantizing levels for 4-bit linear encoding

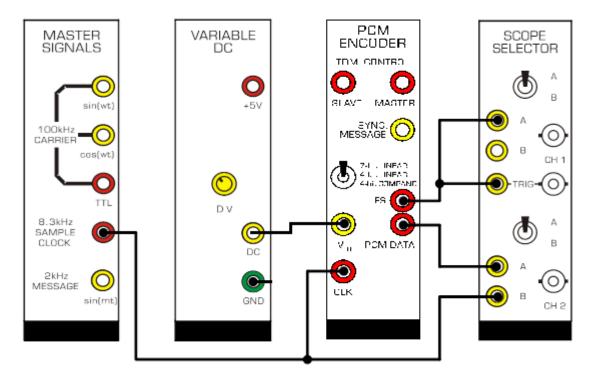

1. Construct the TIMS model of PCM system as shown in below Figure 4.

Figure.4PCM Encoder TIMS Model

- 2. Set the toggle switch to 4-BIT liner. Though standard PCM uses 7 bits, selecting the 4-bit encoding scheme will reduce the number of quantization levels to be examined to 16 only.

- **3.** Feed a DC voltage level from the VARIABLE DC module to Vin of the PCM Encoder . Turn the knob of the variable DC voltage to the least (negative) value (full counterclockwise).

- **4.** Adjust Vin to its maximum negative value. Record the DC voltage. You should be getting all zeros for the 4-bit binary number for this DC setting.

- **5.** Gradually increase the amplitude of the DC input signal until you notice a change to the PCM output. Record the binary sequence of the new digital word, and the input amplitude at which the change occurred.

- **6.** Continue this process over the full range of the DC supply. You should be getting all ones for the 4-bit binary number for this DC setting, **Use** Table 1 to recorded your value.

|      |   |    | - |

|------|---|----|---|

| מיוי | h | _  | 1 |

| 1 4  | n | œ. |   |

| DC voltage | Digital word |

|------------|--------------|

|            |              |

|            |              |

|            |              |

|            |              |

|            |              |

- Sketch the input-output characteristics of the Quantizer. This is a staircase plot, with the input voltage on the x-axis and the output level (labeled as a binary sequence) on the y-axis.

- Connect the corners of the stair steps with the best fit. Is the curve linear?

### Part III: Time-Varying Messages

- **1.** Set the toggle switch to 4-BIT linear.

- 2. Using frequency counter set the audio oscillator about 0.2kHz.

- **3.** Connect the Audio Oscillator output to Vin of the PCM Encoder.

- Observe the PCM Data output over consecutive frames.

- Save the CLK signal, Fs signal, and PCM data in you lab sheet.

# Part IV: PCM Decoding

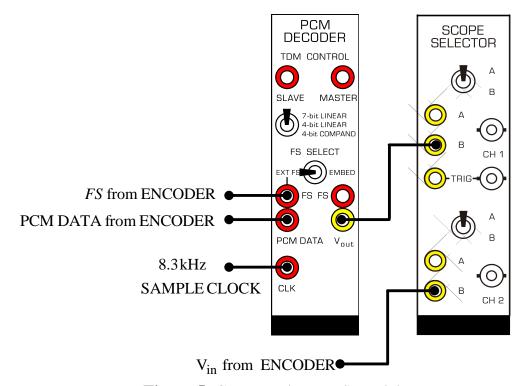

- 1. Borrow the frame synchronization signal FS from the transmitter by connecting it to the frame synchronization input FS of the receiver

- 2. Check that the FS SELECT toggle switch is set to EXT FS(See Figure 5).

- Save the original signal (input to the PCM Encoder) and recovered signal in your lab sheets.

- **3.** Connect the output of the PCM Decoder to a Tunable LPF. Now observe the original signal together with the output of the filter and start adjusting the cutoff frequency.

Figure.5PCM Decoder TIMS Model